- 亿玖动态

- 行业资讯

三星即将推出革命性3D HBM芯片封装技术,或将与台积电打响争夺战

发布时间:2024-06-17

上周在美国硅谷举办的“2024年三星代工论坛”上,三星电子披露了最新的芯片封装技术和服务路线图,这是三星首次在公开活动中详细介绍HBM 芯片的3D封装技术。

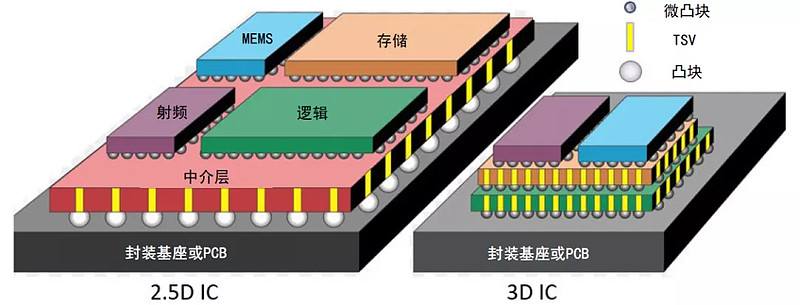

目前,HBM 芯片主要采用2.5D技术封装,通过该技术将硅中间层与逻辑芯片水平连接,而3D芯片封装技术在封装过程将HBM芯片以垂直立体方式堆叠在GPU顶部。这种改变堆叠方式可以缩短芯片之间的距离,加快芯片间的连接速度,从而进一步提升数据学习和推理处理的效率,这项技术也被视作为当前快速增长的AI芯片市场的大创新。

相较于2.5D封装技术,3D封装无需硅中介层或位于芯片之间的薄基板,使得芯片能够实现高效的通信和协同工作。3D封装技术有效地降低了功耗和处理延迟,提高了半导体芯片电信号的质量。早在2023年年底,三星电子就曾透露过关于3D封装技术的部分信息,并将其分为三个类别:SAINT S——垂直堆叠SRAM内存芯片和CPU;SAINT D——涉及CPU、GPU等处理器和DRAM内存的垂直封装;SAINT L——负责堆叠应用处理器(AP),此次的主要命名为SAINT D,即三星先进互连技术-D的简称。三星先进封装团队将垂直互连其存储业务部门生产的 HBM 芯片与其代工部门为无晶圆厂公司组装的GPU,形成”“一站式”解决方案,从而缩短生产周期,提高生产效率。

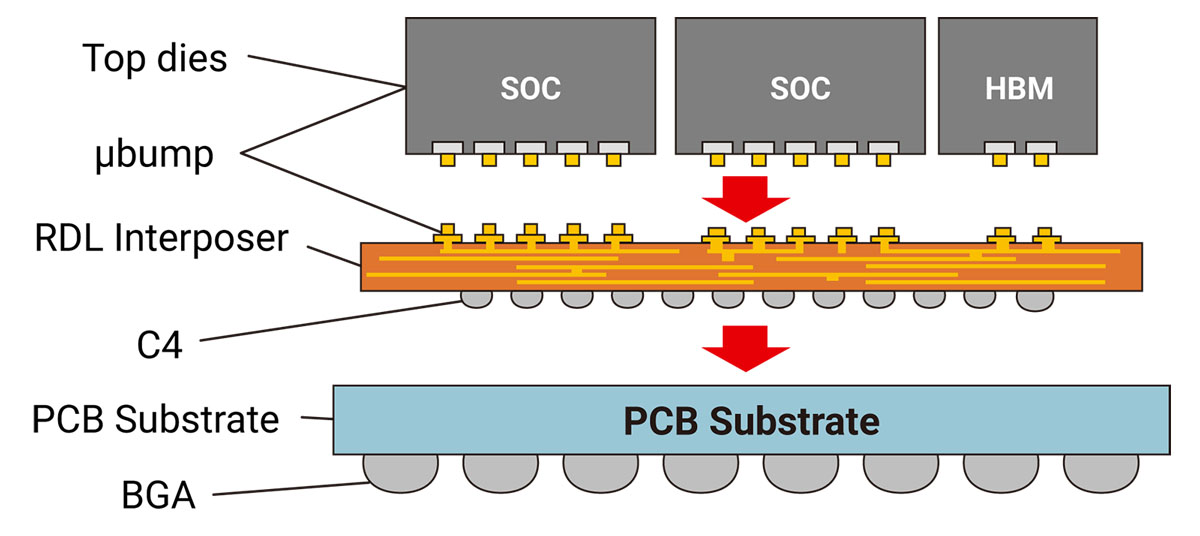

与此同时,台积电作为先进封装技术的领先者,尤其是其CoWoS技术,已经在HBM与CPU/GPU处理器集成的解决方案中占据重要地位。台积电的CoWoS技术是一种2.5D封装技术,它将逻辑芯片和3D的HBM整合成一个模块,再加装到2D封装基板上。此次三星推出的3D HBM芯片封装服务,正是为了迎合AI、高性能计算和HBM的市场需求,因此也将对台积电的市场订单产生一定影响。此外,SK海力士与台积电已经签署了谅解备忘录,共同推进HBM4的研发,并通过先进的封装技术提升逻辑和HBM的集成度,预计HBM4将于2026年开始量产。这样的合作方式会促使台积电带来更先进的封装解决方案,从而提升台积电的市场竞争力,加剧与三星电子在此领域的竞争。

AI和高性能计算的热潮,为整个行业带来了新的机遇和挑战,三星电子与台积电在这场未定数的争夺战中,唯有不断提升自身竞争力,才能保持稳定,稳步前行。